업계 최고 수준 용량·데이터 전송 속도·전력 효율 확보

연내 양산 준비 완료해 내년부터 본격 공급 계획

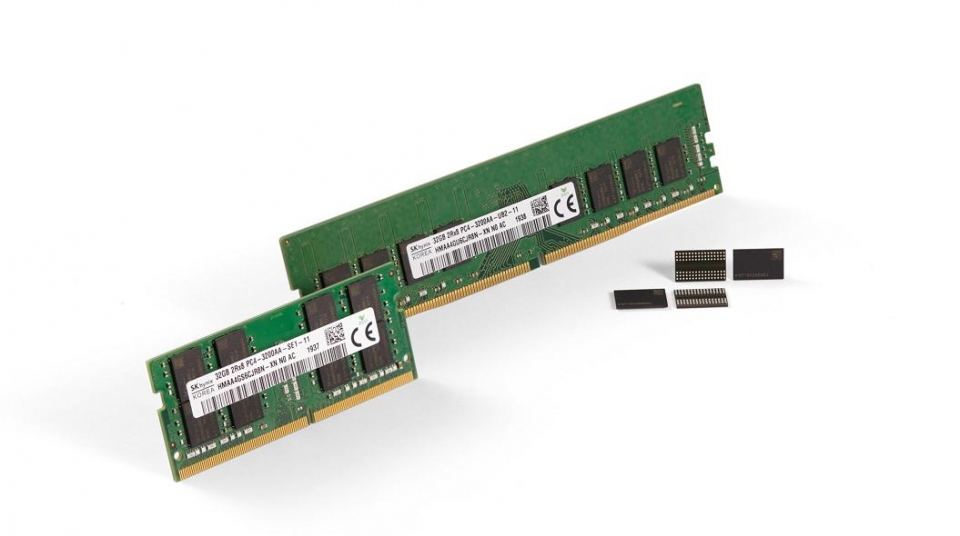

SK하이닉스가 3세대 10나노급(1z나노) 미세공정을 적용한 16Gb DDR4 D램 개발에 성공했다. 2세대 10나노급(1y나노) D램을 개발한지 11개월만이다.

SK하이닉스가 공정 미세화에 갈수록 속도를 붙이고 있는 모습이다.

SK하이닉스는 21일 3세대 10나노급 16Gb(기가비트) DDR4 D램을 개발했다고 밝혔다.

10나노대 D램은 공정에 따라 1세대(1x나노), 2세대(1y나노), 3세대(1z나노)로 나뉜다. 1x나노는 10나노대 후반(18~19나노)공정이다. 1z나노는 10나노대 중반(14~16나노) 공정으로 제조한다.

반도체는 공정이 미세해질수록 생산성이 좋아지고 전력 소모가 줄어든다.

SK하이닉스 1z나노 D램은 단일 칩 기준 업계 최대 용량인 16Gb를 구현했다. 웨이퍼 1장에서 생산되는 메모리 총 용량은 기존 1y나노 D램보다 27% 늘었다.

전력 소모는 2세대 8Gb 제품보다 40%가량 낮다.

데이터 전송 속도는 DDR4 규격 최대인 3200Mbps까지 지원한다. 신규 물질을 적용해 D램 동작 핵심 요소인 정전용량(Capacitance)도 극대화했다. 정전용량이 늘어나면 데이터 유지시간과 정합도가 상승한다. 또 새로운 설계 기술을 도입해 동작 안정성도 높였다.

SK하이닉스는 1z나노 D램 개발에 EUV(극자외선) 노광장비를 사용하지 않았다. 이는 앞서 1z나노 D램을 개발한 삼성전자와 같다.

SK하이닉스 관계자는 "기존 ArF(불화아르곤) 장비를 사용해 원가 경쟁력을 갖췄다"고 설명했다.

SK하이닉스는 차세대 모바일 D램인 LPDDR5와 최고속 D램 ‘HBM3’ 등에 3세대 10나노급 미세공정 기술을 확대 적용할 계획이다.

이정훈 D램개발사업 1z TF장 담당은 "3세대 10나노급 DDR4 D램은 업계 최고 수준 용량과 속도에 전력 효율까지 갖춰, 고성능·고용량 D램을 찾는 수요 변화에 적합한 제품"이라며 "연내 양산 준비를 마치고 내년부터 본격 공급에 나서겠다"고 말했다.