비아 홀 공정없이 패턴화한 절연막 적층…"소자 성능 탁월"

한국과학기술원(KAIST)과 포항공과대(POSTECH) 연구진이 기존 방식에서 벗어난 신개념 3차원(3D) 유기 집적회로를 개발했다.

11일 KAIST에 따르면 임성갑 생명화학공학과 교수와 김재준 포스텍 창의IT융합공학과 교수 공동 연구팀은 비아 홀(via-hole) 공정 없이도 금속을 다중으로 상호 연결할 수 있는 기술을 구현했다.

유기 트랜지스터 기반 집적회로는 구부리거나 접어도 그 특성을 그대로 유지할 수 있다. 유연한 디스플레이나 몸에 두를 수 있는 센서 등에 적용할 수 있다.

다만, 화학적 용매·플라스마·고온 등에 쉽게 손상되는 한계를 보인다.

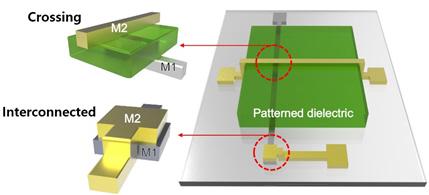

기존에는 유기 트랜지스터 기반 집적회로 구현을 위한 금속 전극 접속 과정에서 절연막 일부에 구멍(비아 홀)을 냈다.

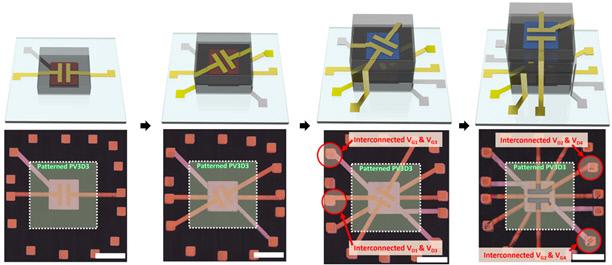

공동 연구팀은 이 방법 대신 패턴화한 절연막을 직접 쌓았다. 이를 통해 5층 이상의 3D 고성능 유기 집적회로를 구현했다.

제작된 트랜지스터는 소자 신뢰성과 균일성 면에서 탁월했다고 연구팀은 설명했다. 비아 홀 공정과는 달리 유기 반도체 소자에 손상을 주지 않았기 때문이다.

연구팀은 또 수직 분포된 트랜지스터를 상호 연결해 인버터·낸드·노어 등 다양한 디지털 논리 회로를 제작했다. 효과적인 금속 상호연결을 위한 레이아웃 디자인 규칙도 제안했다.

김재준 포스텍 교수는 "패턴 절연막을 이용하는 유기 집적회로로 가기 위한 핵심 기술 원천이 됐다"며 "다양한 반도체 집적회로 구현에 핵심적인 역할을 할 것으로 기대한다"고 말했다.

연구는 과학기술정보통신부·한국연구재단·삼성전자 미래기술육성센터 지원을 받아 수행했다.

성과를 담은 논문은 지난 3일 네이처 커뮤니케이션(Nature Communications) 온라인판에 실렸다.